Tiroler Quanten-Startup ParityQC stellt gemeinsam mit IBM neuen Industrierekord auf

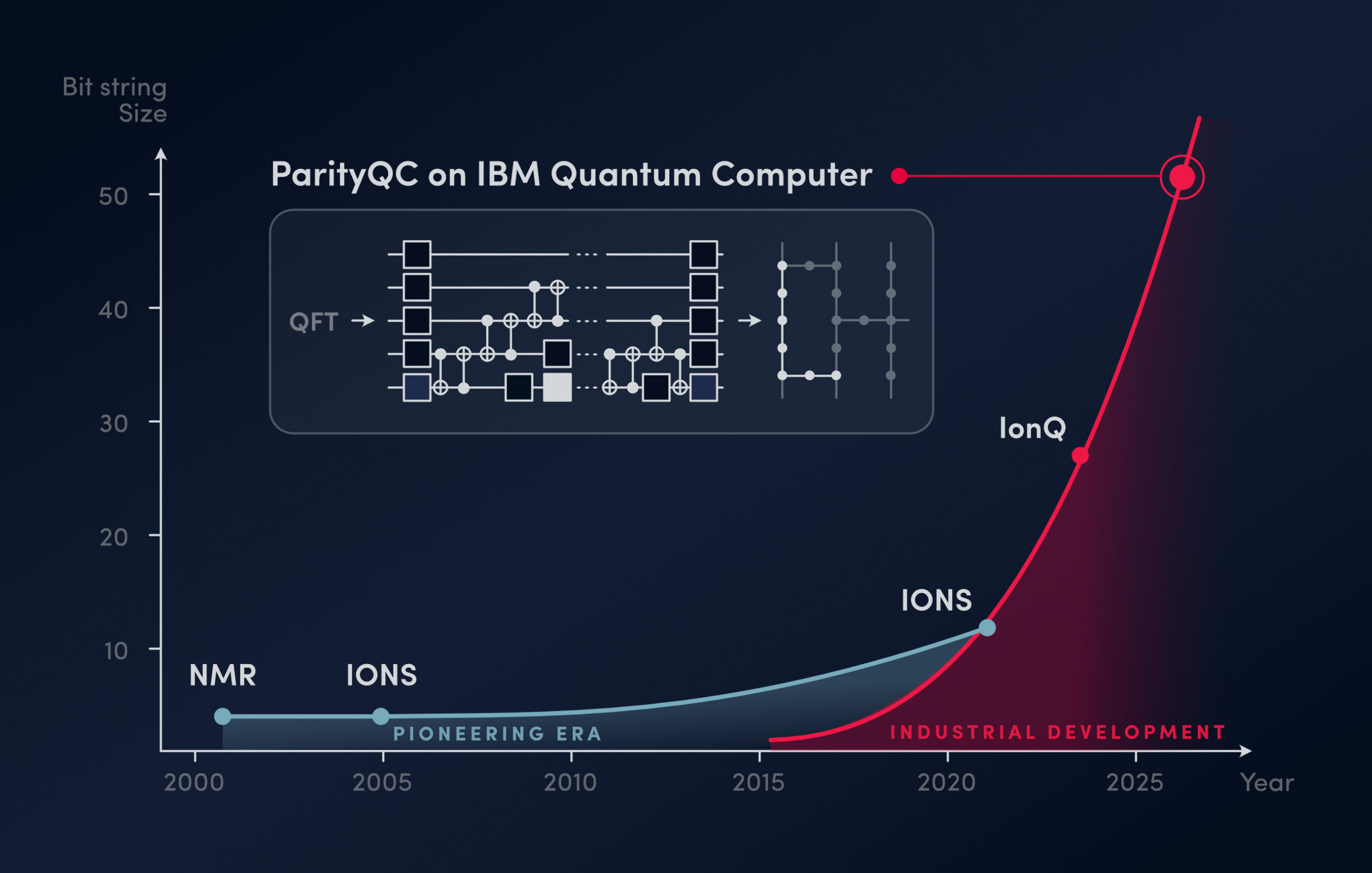

Es ist ein Meilenstein, der die Quantenbranche aufhorchen lässt: ParityQC hat mit einem IBM Quantum Heron Prozessor die größte je dokumentierte Quantum Fourier Transform (QFT) realisiert. 52 supraleitende Qubits kamen dabei zum Einsatz – nahezu doppelt so viele wie beim bisherigen Rekord von 27 Ionenfallen-Qubits, der gerade einmal 24 Monate zurückliegt.

Die QFT ist dabei kein beliebiger Benchmark: Als zentraler Baustein für Anwendungen in der Kryptografie, Finanzmodellierung und Materialwissenschaft gilt sie als eine der wichtigsten Messgrößen für reale Quantenleistung.

Europas Quantenindustrie greift nach der Weltspitze

„Dieser Meilenstein wurde erst durch das Zusammenspiel von IBMs neuester Quantenhardware und der ParityQC Architektur möglich – das hat zu einer exponentiellen Effizienzsteigerung geführt“, erklären Wolfgang Lechner und Magdalena Hauser, Co-CEOs von ParityQC. „Wir erleben gerade, wie europäische Quanteninnovation eine globale Führungsrolle einnimmt, wenn es darum geht, theoretisches Potenzial in reale Leistung zu übersetzen.“

Bemerkenswert ist vor allem die Geschwindigkeit, mit der sich das Feld entwickelt. Was lange als rein akademische Disziplin galt, wird zunehmend zur skalierbaren Industrie – mit einer Dynamik, die an die frühen Jahre der klassischen Computertechnik erinnert.

Hermann Hauser, ParityQC-Investor und Mitgründer von Acorn und ARM, zieht genau diese Parallele: „So wie die Verdopplung der Transistordichte einst die Ära der integrierten Schaltkreise einleitete, markiert die Verdopplung der Quantenrechenkapazität den Eintritt des Quantencomputings in sein eigenes Zeitalter der exponentiellen Skalierung.“

Parity Twine: Der technologische Gamechanger

Hinter dem Rekord steht die sogenannte Parity Twine Architektur von ParityQC – ein Compilation-Ansatz, der die Ausführung von Quantenalgorithmen grundlegend verändert. Die Innovation besteht darin, sowohl die Anzahl der Gates als auch die Schaltkreistiefe drastisch zu reduzieren. Entscheidend dabei: Parity Twine kommt ohne SWAP-Gates aus, die auf vielen Hardware-Plattformen eine der größten Fehlerquellen darstellen.

Das Ergebnis: Algorithmen laufen in weniger Schritten, mit geringerer Rauschakkumulation und deutlich höherer Fidelity. Bei der QFT-Implementierung auf dem IBM Heron r3 Prozessor erreichte das Team die höchste je gemessene Prozessgenauigkeit für eine unitäre QFT mit 52 Qubits – und konnte zeigen, dass der Leistungsvorteil von Parity Twine im Vergleich zu bisherigen Alternativen exponentiell (exp(N²)) mit der Qubit-Anzahl skaliert.

Auch IBM sieht in der Zusammenarbeit großes Potenzial. „ParityQCs Demonstration ihrer Parity Twine Anwendung auf IBM-Quantenhardware ist ein vielversprechendes Beispiel dafür, wie sich die Anwendung auch auf hardware-bewusste Implementierungen von Algorithmen für komplexe, industriell relevante Optimierungsprobleme erweitern lässt“, sagt Scott Crowder, Vice President, IBM Quantum Adoption.

Was das für die Praxis bedeutet

Die Tragweite des Rekords geht weit über einen akademischen Benchmark hinaus. Die Parity Twine Architektur lässt sich für ein breites Spektrum industrieller Anwendungen einsetzen:

In der Pharmaforschung könnte sie die Simulation molekularer Wechselwirkungen beschleunigen, die für die Wirkstoffentwicklung entscheidend sind. Im Finanzsektor eröffnet sie neue Möglichkeiten für hochkomplexe Portfoliooptimierung und Risikomodellierung. In der Materialwissenschaft wird die Simulation komplexer physikalischer Systeme realistisch, die bisher außerhalb der Reichweite klassischer Supercomputer lagen.

Mit anderen Worten: Probleme, an denen heutige Höchstleistungsrechner Jahre scheitern würden – wenn sie sie überhaupt lösen könnten – rücken in greifbare Nähe.

Co-Design als europäischer Weg

ParityQC verfolgt dabei einen eigenständigen Ansatz. Das Unternehmen entwickelt Blaupausen und Software-Umgebungen für skalierbare Quantencomputer und arbeitet in einem Co-Design-Prinzip mit Hardwarepartnern weltweit zusammen. Die ParityQC Architektur reduziert die Komplexität des Hardware-Designs, integriert Fehlerkorrektur und vereinfacht die Konnektivität.

Der aktuelle Rekord untermauert die Strategie: Durch die Kombination der Architektur-Vorteile mit unterschiedlichen Hardware-Plattformen will ParityQC den Pfad des exponentiellen Wachstums aktiv mitgestalten – und zeigt, dass europäische Deep-Tech-Unternehmen im globalen Quantenrennen nicht nur mitspielen, sondern das Tempo vorgeben können.